PT 이슈

협회 및 유관단체

집적회로(Integrated Circuit)는 특정의 복잡한 기능을 위해 복수의 소자를 하나로 묶은 반도체 디바이스(기기)이다. 반도체 디바이스의 집적고밀도화는 성능, 기능, 신뢰성 향상, 1소자(Bit) 당 저비용화 등의 이점을 가지고 있다. 때문에 집적회로 탄생 이래 집적고밀도화 기술개발이 끊임없이 이어져 왔다. 인텔사의 창업자 중 한명인 고든 무어(Gordon Moore)는 이른바 무어의 법칙 “반도체 기능과 집적고밀도화는 18개월 마다 2배가 된다.”라고 경험을 바탕으로 장래예측을 1965년에 발표했다. ULSI는 이후 약 3년 주기로 4배의 집적고밀도화가 진행되었으며, 아직도 무어의 법칙은 건재하다. 이 집적고밀도화를 가능하게 한 것이 미세한 회로 패턴을 형성하는 반도체 리소그래피(Lithography)에 의한 미세 패터닝 기술의 진보 덕분이라고 해도 과언이 아니다.

리소그래피라고 하는 단어의 어원은 판화용어인 “리소그래프”에서 유래되 었다고 한다. 반도체 제조공정에 있어 리소그래피란 마스크(Mask), 정확히 는 템플릿(Template) 원판에 형성된 반도체 디바이스 회로 패턴을 전사장치 를 통해 실리콘웨이퍼 상의 레지스트(Resist)라고 하는 수지 등으로 패턴을 전사하는 기술이다.

차세대 반도체 리소그래피 후보 중 하나인 나노 임프린트 리소그래피(Nano Imprint Lithography (이하 NIL)은 템플릿을 실리콘웨이퍼 상의 레지스트 에 직접 전사하는 기술이다. 반도체 리소그래피가 반도체 제조기술로서 성 립되기 위해서는 반도체 소자를 여러 층 겹쳐 형성하는데, 이때 상대위치 틀 어짐 정도를 말하는 중첩정밀도 (Overlay Accuracy)의 향상, 반도체 회로 오 픈 및 쇼트 등 회로불량 결함(Defect) 저감 등, 다양한 과제의 극복이 필요 하다. 특히 NIL은 템플릿과 웨이퍼 사이에 직접 전사하기 때문에 양산기술 로서 성숙하려면 결함 관리기술로서 나노디펙트 매니지먼트 (Nano Defect Management:NDM)의 기술 혁신이 필요하다.

본고는 NIL의 반도체 양산적용을 위한 최신동향과 과제극복 지침, NDM를 따르는 앞으로의 기술개발 전망 등에 대해서 서술한다.

광리소그래피 변천

반도체 메모리 디바이스 (Memory Device)에서 회로 패턴의 크기는 하프 피치(Half Pitch : hp)로 표기되는 경우가 많다. 반도체 메모리 디바이스에 서는 하프피치의 크기와 회로 패턴의 크기가 대체로 같지만, 로직 디바이스 (Logic Device)에서는 회로 패턴 크기를 노드(Node)로 표기하는 경우가 많 다. 하지만 노드 표기와 회로 패턴 크기는 일치하지 않는 경우가 많으므로 주 의가 필요하다.

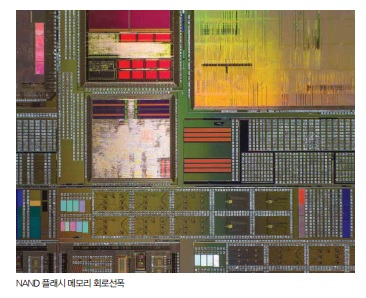

현재 양산되고 있는 NAND 플래시 메모리 최소 하프피치는 20nm hp 이하 에 이르고 있다. NAND 플래시 메모리 최소 하프피치는 인플루엔자 바이러 스 크기보다도 작다.

반도체 디바이스는 단위면적당 회로 소자수 (Bit수/cm2)를 집적함으로써 메 모리 용량의 확대와 1Bit 당 가격 저감이 도모되어 왔다. 이 저비용화 요구 품질을 만족시키기 위해 반도체 회로의 하프피치를 축소하는 리소그래피 기 술개발이 개발되어 왔다. 그러는 동안 미세화 실현의 주역은 광 리소그래피 (Optical Lithography)였다. 광 리소그래피는 마스크상에 그려진 패턴에 빛 을 조사하고, 패턴으로부터 발생한 회절광이 광노광장치의 촬영 렌즈를 통 해 실리콘웨이퍼 상의 레지스트에 광학상을 투영해 패턴을 전사하는 기술이 다. 광 리소그래피에 있어 레지스트란 광화학반응 등으로 패터닝을 실시하 는 감광성 필름의 총칭이다. 광리소그래피에 의한 패턴 미세화는 광노광장 치에 이용되는 파장의 단파장화와 투영렌즈의 개구 크기를 나타내는 지표인 NA(Numerical Aperture : 개구수)의 확대 개발에 의해 진행되어 왔다. 이 처럼 반도체 디바이스는 「리소그래피에 의한 미세화 = 코스트 다운 실현」이 라는 길을 걸어왔다.

광 리소그래피에 따라 패턴이 형성되는 하프칩(hp)은 패턴 형성 해상도 (Resolution)를 말하며, 레일리식 (1)에 따라 (1)해상도 = hp =k1·λ/NA

여기서 λ는 광 파장(nm), NA는 개구수,k1은 프로세스 팩터라고 불리는 정 수이다. 프로세스 팩터 k1의 이론적인 최소값은 파장의 1/4인 0.25가 된다. 단, 프로세스 팩터 k1은 레지스트에 투영되는 광학상과 레지스트에서의 패 턴 형성 충실성능, 디바이스 패턴의 복잡성, 투영광학계 수차, 광학상의 광근 접 효과 오차 등의 광학성능에 의존해 그 값은 커지게 된다. 바꾸어 말하면 k1은 리소그래피에 있어 패턴형성의 어려움을 나타내는 지표라고 해석할 수 있다. 최신 광 리소그래피를 NAND 플래시 메모리에 적용하면 ArF광의 파장 λ=193nm, 개구수 NA=1.35, 프로세스 팩터 k1=0.28 값이라고 하면 ArF 광 리소그래피의 해상한계는 40nm hp 정도가 된다.

따라서 193nm의 파장을 이용한 ArF 엑시머레이저 노광장치는 단파장화 및 고NA화에 관해서는 반도체 디바이스가 요구하는 선폭을 형성하는 것이 불 가능하다. 현재로서는 광 리소그래피를 여러층 겹쳐 패터닝을 실행하는 멀 티 패터닝 (Multi Patterning)이 실제 생산에 사용되고 있다. 즉 20nm hp에 서 40nm hp는 2회 패터닝을 실시하는 더블 패터닝(Double Patterning)을 사용하게 된다. 현재 NAND의 최소 하프칩인 20nm hp 이하의 패터닝에는 멀티패터닝이 사용되고 있다. 이 멀티패터닝은 복수의 노광장치, 복수의 마 스크, 그리고 멀티 패터닝에 부수되는 프로세스에 거액의 투자가 필요하다. 메모리 디바이스의 대량생산에는 막대한 리소그래피 투자가 필요하기 때문 에 저렴한 비용으로 높은 생산성(스루풋)이 나는 리소그래피 프로세스 기술 이 필요하다. ArF 광 리소그래피 멀티 패터닝을 폐기하고, 미세화 및 저비용 의 리소그래피를 실현하는 기술로서 차세대 리소그래피 후보의 하나인 극단 자외선(연X-선광)을 이용하는 EUVL(Extreme Ultra Violet Lithography)이 기대되고 있다. 현재 제품화되어 있는 EUVL은 광원파장 λ=13.5nm, 개구수 NA, 최신 레지스트 성능 등으로부터 프로세스 팩터를 k1=0.3으로 하면 레 일리식(1)로부터 회로 패턴 해상도는 12nm hp 패턴 형성이 이론상 가능하 다. 하지만 EUVL은 안정된 광원 출력, 노광장치 코스트 퍼포먼스(장치가격/생산성), 마스크 결함발생 등 곤란한 과제는 해결에 이르지 못했기 때문에 현 재는 아직 양산기술로서 실현되지 않았다.

멀티패터닝 기술에는 노광장치의 수, 부가된 공정의 증가로 패터닝 도입 비 용은 거액이다. 멀티패터닝 및 EUVL 리소그래피 선택에는 종래의 「리소그 래피에 의한 미세화 = 비용삭감 실현」이라는 길이 성립되지 않고 있다.

반도체제조용NIL원리와과제극복

우리는 미세화라는 기술적 과제와 미세화에 따른 경제성이라는 이율배반의 과제를 극복하기 위해 템플릿에 패턴 형성된 디바이스 패턴을 직접 웨이퍼 에 전사하는 NIL 연구개발을 진행해 왔다. NIL은 디바이스 패턴 원판인 나노 스케일 템플릿(스탬퍼로도 불림)으로 압인(임프린트)에 의해 패턴을 형성하 는 기술이다. NIL은 1995년에 프린스턴 대학의 Chou 교수가 열 임프린트 로 10nm의 레지스트 패턴을 전사한 보고가 있고,2000년에 텍사스 대학의 Willson이 반도체 디바이스에 적용 가능한 NIL기술을 보고하고 있다.

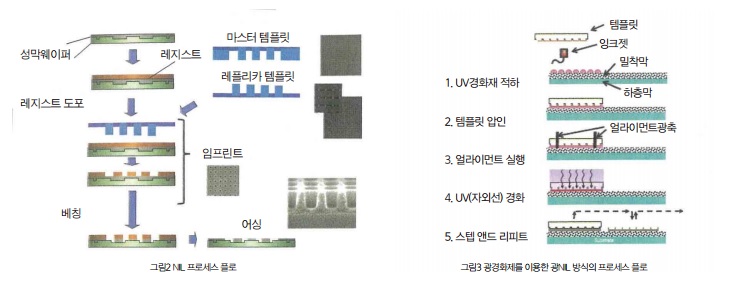

NIL 프로세스 플로를 그림2에 나타낸다. 반도체 디바이스 소자가 되는 소자 재료 실리콘웨이퍼에 막을 형성한 뒤 레지스트를 도포한다. NIL에 있어 레 지스트란 템플릿 압인 후에 패턴이 형성되는 수지이다. 다음으로 템플릿에 회로 패턴을 형성하고, 템플릿을 레지스트에 압인하는 것으로 레지스트 상 에 회로 패턴이 전사된다. 레지스트를 마스크로서 에칭을 실시해 소자재료 에 패턴을 형성해 남은 레지스트를 제거하는 어싱공정을 통해 소자재료에 회로가 형성된다.

NIL 수법에는 열을 이용해 레지스트가 경화되는 열 임프린트, 기계적 압력으 로 레지스트에 패턴을 형성하는 압착 임프린트, 자외광 (UV광) 등의 조사로 레지스트(여기서는 광경화재료)가 경화됨으로써 템플릿 패턴에 따라 패턴을 형성하는 광 NIL 등이 있다 반도체 디바이스 패턴에는 메모리부 및 센서앰프 부 등 패턴 밀도가 다른 영역이 동일면에 배치되므로 NIL 전사된 후에도 형성 되는 패턴 아래에 남는 레지스트 막두께 (Residual LayerThickness : RLT) 를 일정하게 해야 하는 제약이 있다. 광경화형 잉크젯 (IJ) NIL 방식은 자외선경화수지를 디바이스 패턴정보 기초로 잉크젯을 이용해 드롭렛 형태로 웨이 퍼 상에 배치하는 방식이다. 반도체 디바이스 패턴 밀도에 따라 적하되는 레 지스트양을 제어해 RLT를 제어함으로써 반도체 제조용 NIL로는 최적이다. 광경화형 잉크젯 NIL 방식의 프로세스 플로는 그림 3이 나타내는 바와 같이 1) 실리콘웨이퍼 기판 상에 자외선을 조사하면 딱딱해지는 자외선 경화수지 를 디바이스 패턴의 형상에 따라 잉크젯으로 드롭렛 형태로 적하해 배열하 고,2)레지스트 상에 템플릿을 압인해 3)템플릿과 웨이퍼의 위치를 맞추어 넣 는 얼라인먼트 (Alignment)를 실행하고, 4)자외선을 조사해 자외선 경화수지 가 경화된 후 5) 템플릿을 벗겨내(이형) 패턴을 형성한다.

NIL에 따라 전사된 반도체 디바이스에 이용되는 패턴에 따라 직선형상의 29nm hp 미만의 Lineand Space(L&S) 패턴 및 사선 L&S 패턴, 구멍형상 의 직경 25nm φ 미만의 콘택트홀 패턴 및 필러패턴 형성 예를 그림 4에 나 타낸다.

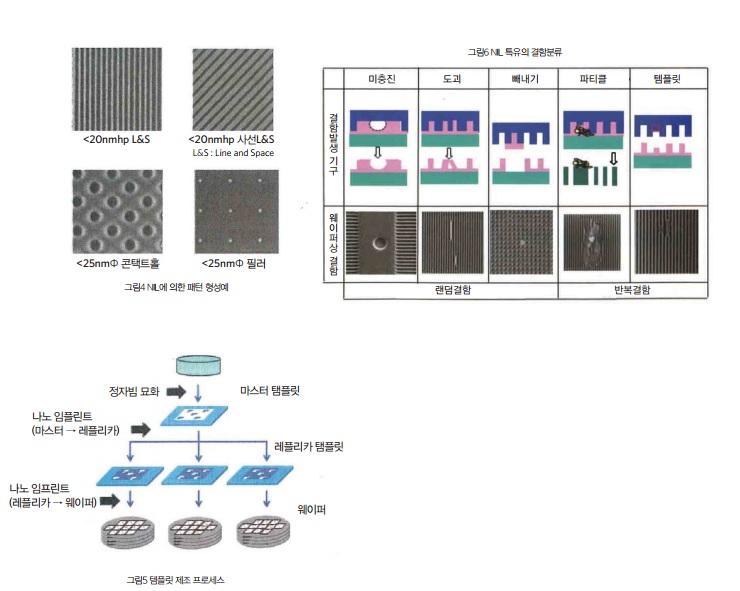

NIL은 템플릿과 웨이퍼 사이가 직접 접촉하는 프로세스이므로 웨이퍼 상 파 티클 등에 의한 템플릿 파손 리스크가 있다. 때문에 사전에 복수의 레플리카 템플릿을 작성해 둔다. 템플릿 제조 프로세스를 그림 5에 타나냈다. 패턴 레 이아웃 정보에 따라 전자빔 마스크 묘화장치에 의해 마스터 템플릿(Master Template)을 제조 후 레플리카 템플릿 (ReplicaTemplate)을 레플리카 템플 릿 작성용 NIL 장치로 제조한다. 실리콘 웨이퍼상의 레지스트 전사는 레플리 카 템플릿을 이용해 실시한다.

NIL 결함발생 메커니즘과대책

NIL 결함은 그림 6에 나타난 바와 같이 크게 랜덤결함과 반복결함으로 분류 된다. 랜덤결함은 주로 미충진 결함, 도괴결함, 빼내기 결함이 많이 발생하고, 레지스트 재료 및 웨이퍼 프로세스 등의 재료 기인으로 랜덤으로 발생하는 결함이다. 반복결함은 주로 NIL을 클린룸 및 장치내 파티클, 템플릿에 부착 한 결함 및 템플릿 자신의 결함에 의해 발생한다. 각각 결함에 대해 결함저감을 위한 방법을 소개한다.

1)미충진 결함

NIL 장치로 전사한 경우 템플릿과 레지스트가 접촉하는 계면에서 나노버블 등의 거품이 발생하는 경우에 미충진 결함이 발생한다. 나노버블은 재료 속 에, 그리고 환경 속에 메탈 이온이 버블표면의 대전과 반응을 해 큰 거품으로 성장하는 경우가 많다. 그림7은 레지스트 속에 메탈이온 혼입 원인으로 발생 하는 미충진 결함의 예이다.

여기서 나타낸 예는 카르본산이 메탈이온과 반응해서 나노버블이 발생, 성장 해 미충진 결함이 된 것이다. 기포가 대전되는 것은 50년 이전부터 알려져 있 었지만 측정곤란 등으로 그 상세는 불명이었다. 특히 레지스트 속의 나노버 블 측정은 곤란하고 앞으로 기술 혁신을 기대하고 싶다. 메탈이온은 레지스 트 재료 자신, 장지배관 계면, 공기중에서 날아와 발생하기 때문에 메탈이온 이 레지스트 등의 재료에 혼입되지 않도록 필터기술 등의 재료정제기술 혁신 이 필요하다. 또 광경화성 수지를 이용한 NIL에서는 템플릿과 레지스트 사이 에 레지스트를 투과하는 가스를 사용하는 경우가 많다. NIL 전사시에 투과성가스가 투과하기 쉬운 재료 설계가 중요하다. 또 템플릿과 웨이퍼 기판 면의 표면 에너지 불균일에 의해 기포결함이 발생하는 경우가 있으므로 기포결함 이 발생하지 않는 재료 설계가 중요하다.

2)도괴결함

NIL장치로 전사를 해 템플릿을 빼낼 때에 레지스트 패턴이 무너지는 현상이 다. 레지스트 파괴 역학적인 강도설계, 템플릿 표면의 레지스트 마찰, 장치 빼 내기 동작 등을 고려한 장치 및 재료설계가 필요하다.

3) 빼내기 결함

NIL장치로 전사를 해 템플릿을 만들 경우 레지스트 패턴을 무리하게 잡아당 겨 발생하는 현상이다. 레지스트 강성, 템플릿 표면의 레지스트 마찰, 장치 빼 내기 동작, 레지스트 기판의 밀착성을 고려해 재료설계가 필요하다.

4)파티클

큰 파티클이 템플릿면 및 웨이퍼면에 날아오면 템플릿이 전사시에 파괴된다. NIL장치 자신이 결함혼입을 막는 기구, 결함검사, 세정기술 혁신이 필요하다.

5)템플릿 결함

템플릿 상에 발생하는 결함으로 주로 템플릿을 제조하는 과정에서 발생하는 결함이다. 또 NIL장치의 전사 시에 발생하는 빼내기 결함도 템플릿 결함이 되어 출현된다. 템플릿 자신의 결함저감을 지원하는 전자빔 묘화장치, 레지 스트, 에칭가공, 결함검사, 결함수정, 세정기술 등의 템플릿 인프라기술에 있 어 결함관리 기술혁신이 필요하다.

나노디펙트매니지먼트

NIL에 한하지 않고 다양한 패터닝에 있어 결함저감은 생산성 향상 및 성능향 상의 관점에서 앞으로 점점 중요해 질 것은 말할 필요도 없다. 반도체에서는 미세화에 따라 보다 작은 결함을 관리해가는 기술 혁신이 필요하다. 예를 들 어 로직 디바이스에서는 2020년 이후 패턴 사이즈는 10nm를 밑돈다고 상 정하면 결함 크기 10nm 이상의 것은 제거할 필요가 있다. 미세한 결함을 검 사하고, 결함이 발생하지 않는 재료, 장치 및 제품을 개발하고, 결함이 발생 한 경우 결함발생 피해를 최소한으로 해 반도체 디바이스를 생산한 제품 속 에 차지하는 소정의 성능을 높이는 수율향상 활동을 나노 디펙트 매니지번트 (NDM:Nano Defect Management)라고 한다. NDM은 많은 요소기술의 복 합체이므로 앞으로 반도체 디바이스 발전은 미세화만이 아니라 NDM 개발 을 세계적 규모로 연계해서 강화해가야할 필요가 있다.

NDM기술의 개념은 그림8에 나타내는 바와 같이 결함검사기술의 혁신(In -spection), 결함발생 인자의 관찰(Monitoring), 결함발생 억제기술(Filter), 결 함이 발생하지 않는 재료(Material), 결함 제거(Cleaning), 환경 청결화(Su-per Cleaning Circumstance), 기계학습 등의 AI(Artificial Intelligence)에 의 한 결함제어기술 영역으로 분류된다.

1) 결함검사기술의혁신(Inspection)

10nm 이하의 결함검사를 실시하기 위해 종래의 광을 이용한 검사로부터 전 자빔(Electron Beam, EB) 등을 이용한 미세검사기술 개발. 메모리 디바이스 의 3차원화에 적합한 결함검사기술이 개발.

2) 결함발생인자의 관찰(Monitoring)

나노버블 발생인자의 메탈이온 검사, 나노버블과 다른 결함분류, 액속 파티 클 관찰기술 개발

3) 결함발생 억제기술 개발

유체 속 및 재료 내의 결함을 제거하는 필터(Filter), 배관, 부품에서 발생하는 파티클 원인해명과 제거기술 개발.

4) 결함이 발생하지 않는재료(Material)

레지스트의 에칭내성 메카니즘 해명과 내에칭성 레지스트 재료, 내에칭성 향 상 프로세스 기술 개발.

5) 결함 제거(Cleaning)

메탈 등의 물리적, 유기물 등의 화학적 파티클 발생원인을 해명하고 제거하 는 세정기술.

6)환경 청결화(SuperCleaningCircumstance)

클린룸, 장치내 및 국소공간에 있어 결함제어를 실시하는 환경 청결화 기술 의 개발

7)AI에의한 결함제어(ArtificailIntelligence)

상기의 기술개발은 종래에도 노력해왔던 개념이었지만,20nm 이상의 결함 사이즈 세계에서는 유체와 고체의 계면 사이에서 지금까지의 물리로는 설명 할 수 없는 현상도 다발하고 있어 기계학습(Deep Learning) 등을 이용한 인 간의 경험에 의지하고 있던 AI에 의한 결함분류 및 결함제어인자의 발견과 과제해결을 실시하는 등의 신규기술개발도 가속화될 것이 틀림없다.

NIL의 전망

NIL은 고품질 미세패턴을 저비용으로 형성하는 것이 용이하고, 실제 반도체 디바이스 양산에 적용을 시작하려고 한다. 양산화 실현에는 결함저감, 중첩 정밀도 요구목표 도달이 필수이다. 특히 NDM 혁신은 NIL의 양산전개에 있 어 점점 더 중요해질 것이다. NIL의 전망을 그림 9에 나타냈다.

반도체 디바이스에 적용된 NIL은 먼저 콘택트홀에 적용 및 멀티패터닝 폐기 (NIL 싱글노광)를 목표로 한다. NIL 기술개발과 호응하는 NDM 기술개발 혁 신이 이루어지면서 리소그래피 결함저감이 비약적으로 향상되고 있고, NIL 은 메모리 디바이스만이 아니라 로직 디바이스에도 적용되고 있다. 더욱이 NIL 전사 화각을 넓혀 스루풋을 올리는 등, 생산성 향상을 목표로 하 고 있다.

본고는 주로 메모리 디바이스 적용의 NIL 기술에 대해 소개했다. 메모리 디 바이스는 오랫동안 미세화 반도체의 고밀고집적화를 견인해 왔지만 메모리 디바이스가 3차원화로 옮겨감에 따라 미세화 진화는 둔화되는 경향이라고 생각된다. 하지만 메모리 디바이스의 패터닝에 의한 비용 저감은 미세화뿐만아니라 다른 디바이스 설계자로부터도 계속 요구되고 있다. 메모리 디바이스 는 결함으로 인해 회로에 불량이 발생해도 회로불량을 회피해 디바이스 기능 을 구제하는 리던던시라고 하는 시스템이 탑재되어 있는 등 결함에 강한 디 바이스 설계가 이루어져 있다. 로직 디바이스는 리던던시 시스템이 탑재되지않기 때문에 결함에 대한 관리가 메모리 디바이스는 엄격하다. NIL 반도체 적 용은 로직디바이스 보다 메모리 디바이스 적용이 간단하다. 반도체 디바이스 는 그 탄생부터 결함과 끝나지 않는 전쟁이었다. 미래를 향해 더 나은 NDM 기술개발이 진행시켜 로직 디바이스의 NIL 양산적용을 목표로 하고 있다

우리는 NIL 개발을 반도체 제조응용에 특화되어 개발을 이어왔다. 앞으로 는 반도체 제조의 NIL 기술로 축적된 기술을 응용해 반도체만이 아니라 MEMS(Micro Electro Mechanical System), 광학부품, 의료분야에서의 3차 원 패턴 가공, 프린티드 일렉트로닉스(Printed Electronics)를 응용한 플렉시 블 디바이스 (Flexible Device) 등, 모든 패터닝 분야에 적용범위 확대를 위해 다양한 새로운 패턴닝 기술 혁신을 수행하고 있다.

장치,재료,검사계측,제조사 연계

반도체 리소그래피의 요구품질은 미세화만이 아닌 생산성, 비용, 수율의 관 점에서 더 까다로워지고 있다. 이와 같은 환경변화 속에서 우리는 반도체 제 조용 NIL 개발을 진행해 왔다. NIL의 양산공장 전개 및 성능 향상은 NDM 혁 신에 관계하며, NDM 각 요소기술의 창성, 혁신이 없으면 NIL의 진화는 없다. 앞으로 NIL 기술의 전개 및 NDM 기술혁신에는 장치, 재료, 검사계측, 디바이 스 제조사의 밀접한 연계가 불가결해질 것이다.