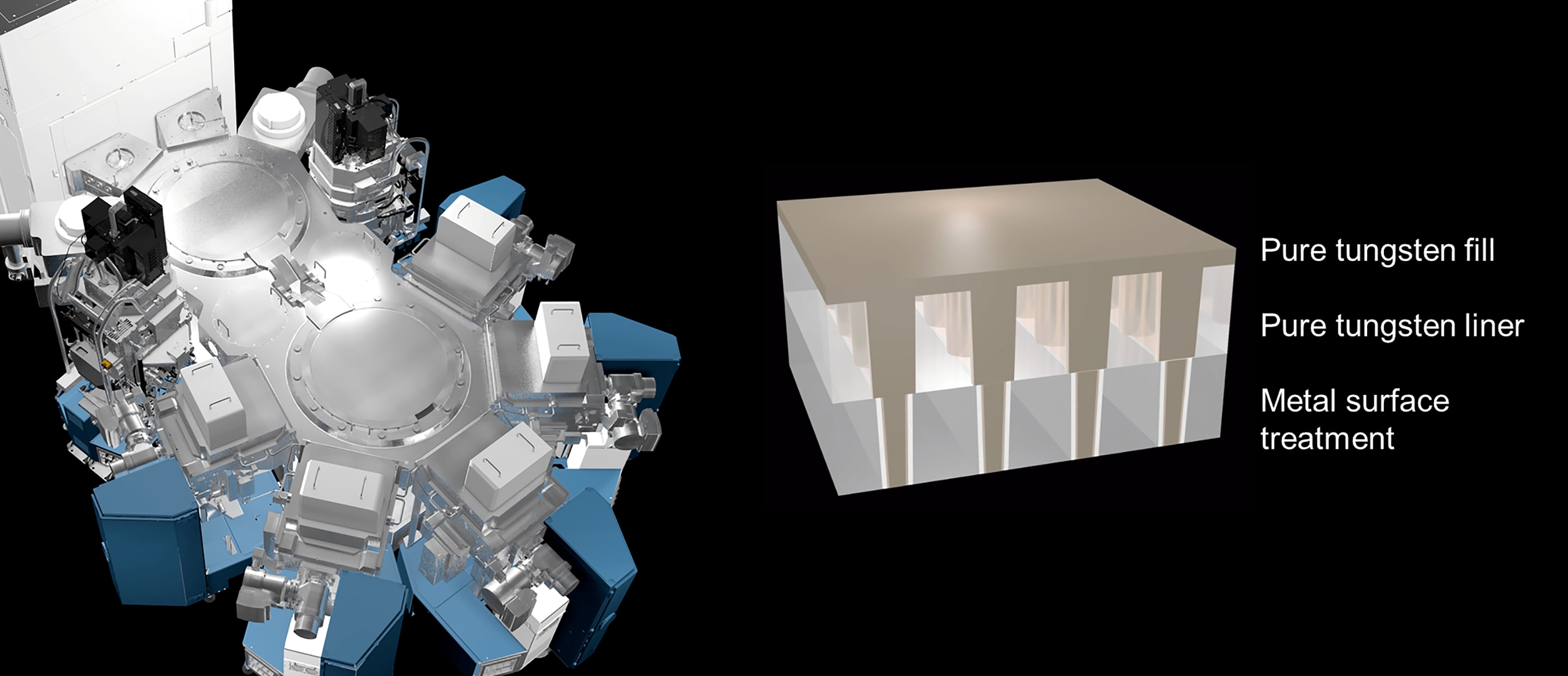

어플라이드 엔듀라 아이오닉 PVD 시스템

어플라이드 머티어리얼즈(Applied Materials)가 트랜지스터 금속배선 증착을 리엔지니어링해 칩 성능 및 전력 개선에 주요 병목이 되는 전기 저항을 크게 줄여주는 새로운 시스템을 발표했다.

반도체 제조사는 칩을 3nm 노드 이하로 미세화하기 위해 첨단 리소그래피 기술을 사용한다. 그러나 선폭이 얇아짐에 따라 전기 저항이 대폭 증가, 반도체 칩 성능은 저하되고 전력 소비는 높아진다. 이러한 금속배선 저항을 그대로 두면 첨단 트랜지스터의 이점이 사라지게 된다.

칩 금속배선은 절연체(dielectric material) 안으로 식각되어 형성되는 트렌치(trenches)와 비아(vias) 안에 증착된다. 기존 방식으로는 이 금속배선이 메탈 스택을 사용해 증착되는데, 메탈 스택에는 메탈이 절연체에 혼합되는 것을 방지하는 장벽층, 접합을 증진하는 라이너층, 메탈 주입을 촉진하는 시드층, 트랜지스터 전극에 사용되는 텅스텐 또는 코발트 등의 메탈, 상호연결용 와이어를 위한 구리가 포함된다. 하지만 장벽과 라이너는 트렌치 및 비아와 달리 미세화가 잘 되지 않아 전도성 메탈이 사용할 수 있는 공간이 줄어든다. 또한 금속배선이 미세 해질수록 전기 저항은 높아진다.

아이오닉 PVD 시스템(Ioniq PVD System)은 어플라이드의 통합 소재 솔루션(IMS)으로 단일 고진공 시스템에서 PVD(물리기상층작) 및 CVD(화학기상증착) 공정과 함께 표면처리 공정도 지원한다. 반도체 제조사가 아이오닉 PVD를 사용하면 질화 티타늄 소재로 만들어지는 고저항 라이너 및 장벽층을 100% 순도의 저저항 PVD 텅스텐 박막으로 대체하고 CVD 텅스텐과 결합시켜 100% 순도의 텅스텐 메탈 전극을 생성할 수 있다. 이 솔루션을 사용하면 저항 문제를 해결하고, 2D 공정미세화를 3nm 노드 또는 그 이하로 구현할 수 있다.

프라부 라자(Prabu Raja) 어플라이드 머티어리얼즈 반도체 프로덕트 그룹 부사장 겸 총괄 매니저는 “전기 저항을 해결하는 어플라이드의 최신 혁신은 재료 공학이 지속적인 2D 미세공정화를 어떻게 실현하는지 보여주는 좋은 사례”라며 “혁신적인 아이오닉 PVD 시스템은 트랜지스터 성능을 떨어뜨리는 병목 현상을 제거해 트랜지스터 운용 속도를 높이고 전력 손실을 줄여준다. 반도체가 계속해서 복잡해짐에 따른 고객들의 고성능 및 저전력 목표 달성을 지원하기 위해서는 고도의 진공 상태에서 여러 공정을 통합하는 역량이 금속배선 분야의 혁신으로 매우 중요해지고 있다”고 말했다.