지멘스가 반도체 패키징·테스트 위탁업체인 SPIL과 협력해 SPIL의 첨단 IC 패키징 기술인 ‘팬아웃웨이퍼레벨패키지(FOWLP)’ 방식이 적용된 새로운 IC 패키지 어셈블리 플래닝 및 3D LVS(Layout versus Schematic) 어셈블리 검증 워크플로우를 개발 및 구현했다.

지멘스 디지털 인더스트리 소프트웨어, 지멘스 EDA 사업부(http://www.siemens.com/eda)는 오늘, 세계유수의 반도체 패키징·테스트 위탁(OSAT) 업체인 SPIL(Siliconware Precision Industries Co., Ltd.)과 협력하여 SPIL의 첨단 IC 패키징 기술인 ‘팬아웃웨이퍼레벨패키지(FOWLP)’ 방식이 적용된 새로운 IC 패키지 어셈블리 플래닝 및 3D LVS(Layout versus Schematic) 어셈블리 검증 워크플로우를 개발 및 구현했다고 발표했다. SPIL은 이와 같이 차별화된 워크플로우를 2.5 및 팬아웃 패키지 제품군에 전반적으로 적용할 계획이다.

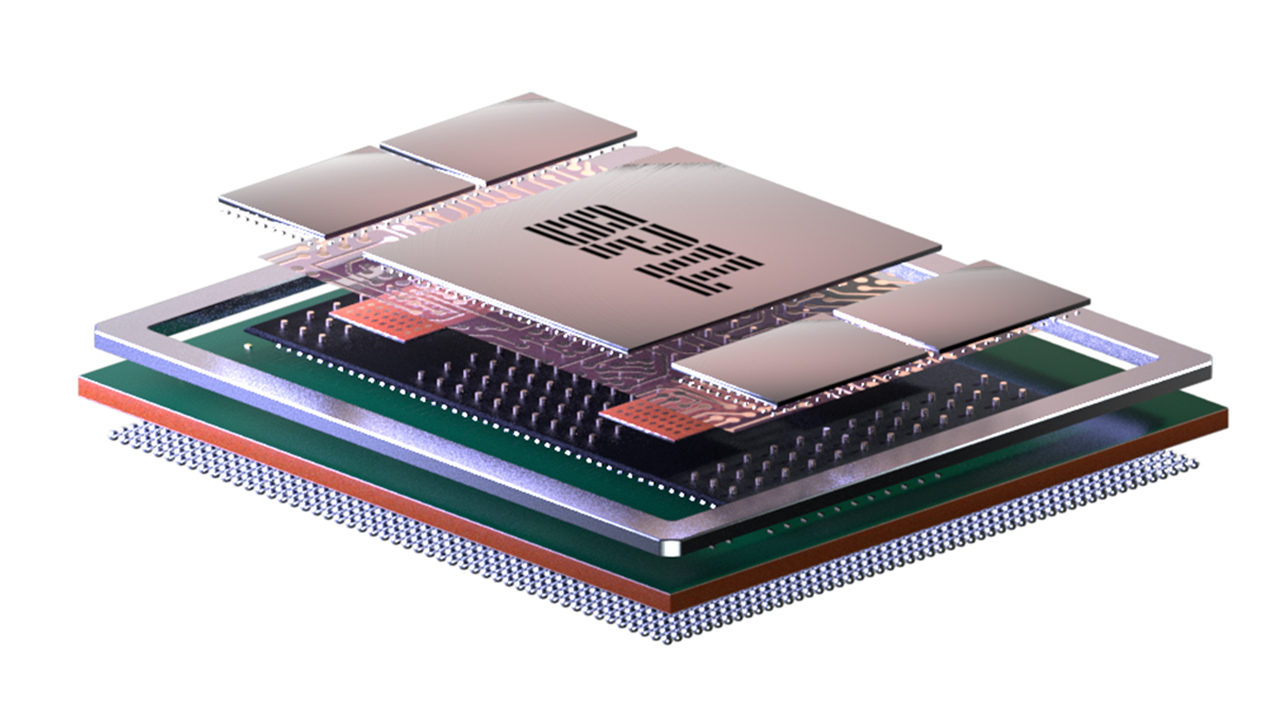

전 세계적으로 보다 높은 성능과 낮은 전력소비를 보다 작은 점유면적으로 제공하는 IC에 대한 수요가 커지는 추세이다. 이러한 추세에 부응하기 위해 IC 설계에는 2.5D 및 3D 구성과 같은 정교한 패키징 기술이 적용되는 경향이 갈수록 증가하고 있다. 이러한 기술은 증가된 I/O 및 회로 밀도를 갖는 다양한 기능의 IC를 하나 이상 결합시키는데, 이를 위해서는 다수의 어셈블리 및 LVS, 연결성, 지오메트리 및 컴포넌트 간격 시나리오를 생성하고 검토할 수 있어야 한다. SPIL은 고객이 이러한 첨단 패키징 기술 적용 관련문제를 해결할 수 있도록 지멘스의 Xpedition™ Substrate Integrator 소프트웨어와 Calibre 3DSTACK 소프트웨어를 패키지 플래닝과 첨단 팬아웃 제품군의3D 패키지 어셈블리 검증 LVS에 적용했다.

SPIL의 CRD 부문 부사장인 Yu Po Wang 박사는 “우리의 해결 과제는 포괄적인 3D LVS를 포함하는 입증된 첨단 패키징 어셈블리 플랜 및 검증 워크플로우를 개발해 적용하는 것이었다”라고 말하며, “지멘스는 이 분야에서 인정받는 선두 업체로서 강력하고 입증된 워크플로우를 갖추고 있다. 이를 우리 생산 부문의 팬아웃 제품군 기술 검증에 사용할 것이다”라고 말했다.

SPIL의 팬아웃 패키징 제품군은 보다 많은 수의 I/O를 반도체 영역에 배선하고 패키지 크기를 팬아웃 프로세스로 확장할 수 있는 추가 공간을 제공한다. 이는 기존의 첨단 패키징 기술로는 달성할 수 없다.

지멘스 디지털 인더스트리 소프트웨어의 EBS(Electronic Board Systems) 부문 부사장(SVP)인 A.J. 인코르바이아(A.J. Incorvaia)는 “지멘스는 SPIL과 협력해 이들의 첨단 패키징 기술에 필요한 워크플로우와 기술을 정의하고 제공하게 된 것을 기쁘게 생각한다”고 말하며, “SPIL의 고객들이 더욱 복잡한 설계를 개발해나감에 따라 SPIL과 지멘스는 이처럼 갈수록 더 정교해지는 설계를 시장에 출시하는 데 필요한 첨단 워크플로우를 제공할 준비를 갖추고 있다”라고 밝혔다.